インテル、AMDなどの10社は3月2日(現地時間)、半導体のダイ間の相互接続のためのオープン規格「Universal Chiplet Interconnect Express」(UCIe)を推進する業界団体の設立と、同規格に基づく標準仕様「UCIe 1.0」を発表した。

参加企業は、Advanced Semiconductor Engineering、AMD、Arm、Google Cloud、インテル、メタ、マイクロソフト、クアルコム、サムスン、TSMC(台湾積体電路製造)の10社で、半導体大手、ファウンドリ企業、パッケージング、IPサプライヤー、クラウドプロバイダーなどが参加している。

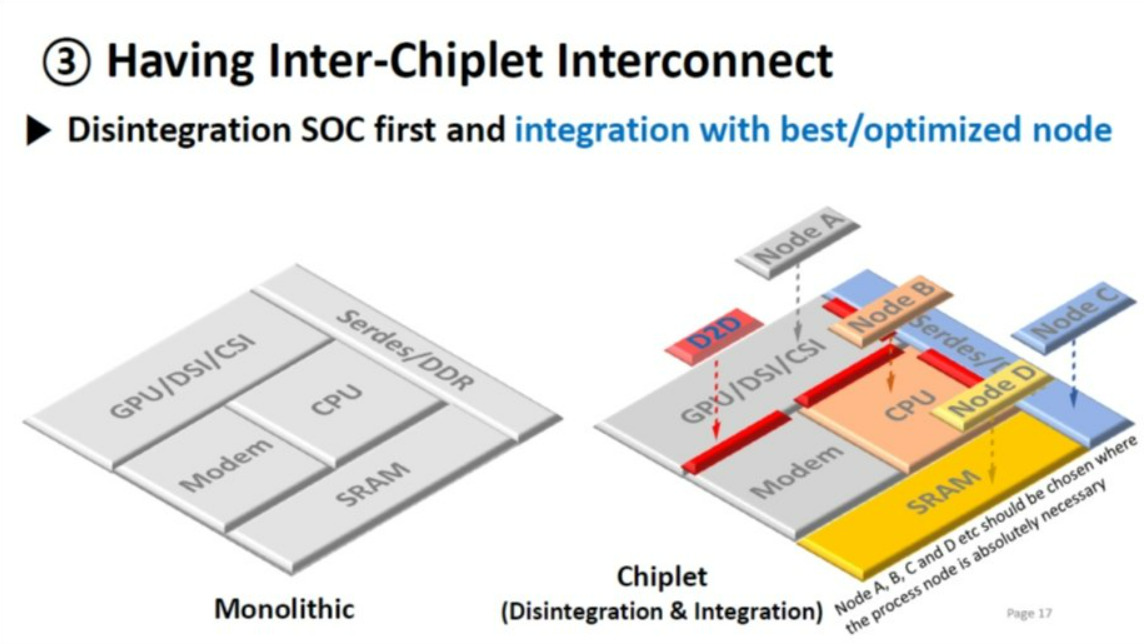

UCIeは、「チップレット」と呼ばれる半導体のダイ上のモジュールを相互接続するための標準仕様。チップレットとは、従来の半導体がパッケージ上のすべての要素をモノリシックに設計・製造していたのに対して、CPUやGPU、SRAMなどの要素を個々に設計・製造し、インテグレーションによって1つの半導体にする設計・製造概念を指す。異なる設計、異なる製造、異なるパッケージング技術のダイであっても相互接続できるのが大きな特徴である。

チップレットを採用したチップは、既に複数のメーカーからリリースされている。今回のUCIeは、業界標準のチップレット仕様を策定し、各社が共通に利用できるようにする点に大きな意義がある。この種の業界標準としてはPCIeやUSBなどの成功例がある。

UCIe 1.0は、ダイ・ツー・ダイ間の物理I/O層やプロトコル、およびソフトウェア・スタックを対象とした標準仕様である。今後、ダイやパッケージの物理的な仕様・規格(フォームファクタ)や管理、セキュリティなどのプロトコルの標準仕様の策定を計画しているという。

チップレット採用の効果としては、半導体製品の市場投入までの時間短縮や、製品およびプロジェクトのコスト低減が期待されている。

インテルのカート・レンダー氏(I/Oテクノロジー・ソリューション・チーム、ストラテジスト)は、「チップレットのようなモジュール式の標準仕様があることによって、半導体アーキテクトは最適な技術を組み合わせて設計するという、とてつもない柔軟性を得ることができる」とし、「次の10年、さらにその先まで、ムーアの法則を拡張する鍵はチップレットにあると確信している」と述べている。

・UCIeサイト

https://www.UCIexpress.org

・UCIeホワイトペーパー

https://www.uciexpress.org/_files/ugd/0c1418_c5970a68ab214ffc97fab16d11581449.pdf

・カート・レンダー氏のブログ「ムーアの法則の未来に向けたチップレットエコシステムの醸成(Fostering a Chiplet Ecosystem for the Future of Moore’s Law)」(英文)

https://www.intel.com/content/www/us/en/newsroom/opinion/fostering-chiplet-ecosystem-future-moores-law.html#gs.s6ykxn

[i Magazine・IS magazine]